- 您现在的位置:买卖IC网 > Sheet目录368 > W9412G6IH-5 (Winbond Electronics)IC DDR-400 SDRAM 128MB 66TSSOPII

W9412G6IH

9.5

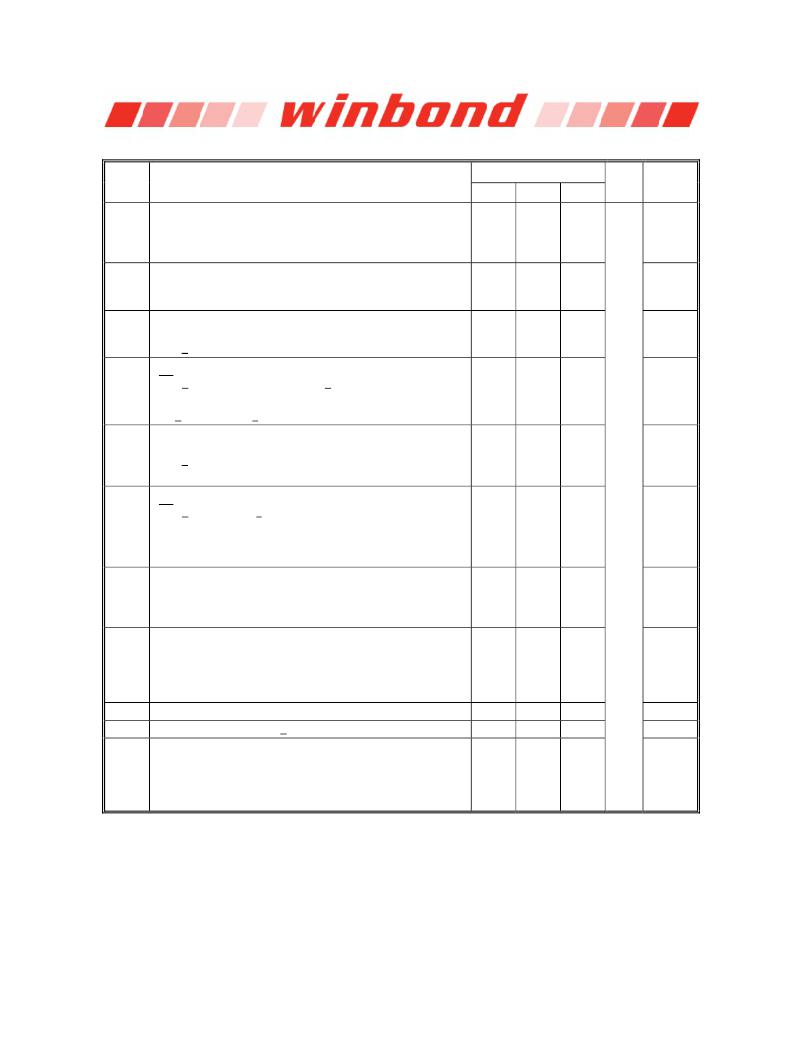

DC Characteristics

SYM.

PARAMETER

-4

MAX.

-5/-5I

-6/-6I

UNIT

NOTES

Operating current: One Bank Active-Precharge;

I DD0

t RC = t RC min; t CK = t CK min;

DQ, DM and DQS inputs changing once per clock cycle;

130

130

120

7

Address and control inputs changing once every two clock cycles.

Operating current: One Bank Active-Read-Precharge;

I DD1

Burst = 4; t RC = t RC min; CL = 3; t CK = t CK min; I OUT = 0 mA;

140

140

130

7, 9

Address and control inputs changing once per clock cycle .

Precharge Power Down standby current:

I DD2P

All Banks Idle; Power down mode;

20

20

20

CKE < V IL max; t CK = t CK min; Vin = V REF for DQ, DQS and DM .

Idle standby current:

I DD2N

CS > V IH min; All Banks Idle; CKE > V IH min; t CK = t CK min;

Address and other control inputs changing once per clock cycle;

45

45

45

7

Vin > V IH min or Vin < V IL max for DQ, DQS and DM .

Active Power Down standby current:

I DD3P

One Bank Active; Power down mode;

CKE < V IL max; t CK = t CK min;

20

20

20

Vin = V REF for DQ, DQS and DM .

Active standby current:

CS > V IH min; CKE > V IH min; One Bank Active-Precharge;

mA

I DD3N

t RC = t RAS max; t CK = t CK min;

60

60

60

7

DQ, DM and DQS inputs changing twice per clock cycle;

Address and other control inputs changing once per clock cycle .

Operating current:

I DD4R

Burst = 2; Reads; Continuous burst; One Bank Active;

Address and control inputs changing once per clock cycle;

185

180

170

7, 9

CL=2; t CK = t CK min; I OUT = 0mA.

Operating current:

Burst = 2; Write; Continuous burst; One Bank Active;

I DD4W

Address and control inputs changing once per clock cycle;

185

180

170

7

CL = 2; t CK = t CK min;

DQ, DM and DQS inputs changing twice per clock cycle.

I DD5

I DD6

Auto Refresh current: t RC = t RFC min.

Self Refresh current: CKE < 0.2V; external clock on; t CK = t CK min.

200

3

200

3

190

3

7

Random Read current: 4 Banks Active Read with activate every

20nS, Auto-Precharge Read every 20 nS;

I DD7

Burst = 4; t RCD = 3; I OUT = 0mA;

DQ, DM and DQS inputs changing twice per clock cycle;

320

320

300

Address changing once per clock cycle.

Publication Release Date: Sep. 16, 2009

- 25 -

Revision A06

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W9412G6JH-5I

IC DDR SDRAM 128MBIT 66TSOPII

W9425G6EH-5

IC DDR-400 SDRAM 256MB 66TSSOPII

W9425G6JH-5I

IC DDR SDRAM 256MBIT 66TSOPII

W947D2HBJX5E

IC LPDDR SDRAM 128MBIT 90VFBGA

W948D2FBJX5E

IC LPDDR SDRAM 256MBIT 90VFBGA

W949D2CBJX5E

IC LPDDR SDRAM 512MBIT 90VFBGA

W971GG6JB25I

IC DDR2 SDRAM 1GBIT 84WBGA

W971GG8JB-25

IC DDR2 SDRAM 1GBIT 60WBGA

相关代理商/技术参数

W9412G6JH

制造商:WINBOND 制造商全称:Winbond 功能描述:2M ? 4 BANKS ? 16 BITS DDR SDRAM

W9412G6JH-4

制造商:Winbond Electronics Corp 功能描述:8*16B DDR1 制造商:Winbond Electronics Corp 功能描述:IC DDR SDRAM 128M 250MHZ 66TSOP

W9412G6JH-5

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR SDRAM 128M-Bit 8Mx16 2.5V 66-Pin TSOP 制造商:Winbond Electronics Corp 功能描述:128M BIT DDR1

W9412G6JH-5I

功能描述:IC DDR SDRAM 128MBIT 66TSOPII RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:72 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 同步 存储容量:4.5M(256K x 18) 速度:133MHz 接口:并联 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x20) 包装:托盘

W9412G6JH-5TR

制造商:Winbond Electronics Corp 功能描述:128M DDR SDRAM X16 200MHZ, 65N

W942

制造商:Performance Tool 功能描述:6 Piece Hook and Pick Set 制造商:PERFORMANCE TOOLS 功能描述:6 PC HOOK AND PICK SET

W942508BH

制造商:未知厂家 制造商全称:未知厂家 功能描述:DRAM

W942508CH

制造商:WINBOND 制造商全称:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM